## **User's Hardware Manual**

# **GX1LCD**

## **Boards**

Ver. 1.3 – 19. September 2002.

#### **Document revision history.**

| Revision | Date           | By  | Comment                                                          |

|----------|----------------|-----|------------------------------------------------------------------|

| 1.0      | 14. July. 2001 | PJA | Initial release                                                  |

| 1.1      | 9. Nov. 2001   | PJA | Production update                                                |

| 1.2      | 21. May. 2002  | JSN | Manual update                                                    |

| 1.3      | 19.Sept. 2002  | PJA | EN60950 requirement added. Inside renamed to Kontron Technology. |

#### **Copyright Notice :**

Copyright © 2002, KONTRON Technology A/S, ALL RIGHTS RESERVED.

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose, without the express written permission of KONTRON Technology A/S.

#### **Trademark Acknowledgement :**

Brand and product names are trademarks or registered trademarks of their respective owners.

#### **Disclaimer :**

KONTRON Technology A/S reserves the right to make changes, without notice, to any product, including circuits and/or software described or contained in this manual in order to improve design and/or performance. KONTRON Technology assumes no responsibility or liability for the use of the described product(s), conveys no license or title under any patent, copyright, or mask work rights to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described in this manual are for illustration purposes only. KONTRON Technology A/S makes no representation or warranty that such application will be suitable for the specified use without further testing or modification.

### **Life Support Policy**

KONTRON Technology's PRODUCTS ARE NOT FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT EXPRESS WRITTEN APPROVAL OF THE GENERAL MANAGER OF KONTRON Technology A/S.

As used herein :

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into body, or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labelling, can be reasonably expected to result in significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### Kontron Technology Technical Support and Services

If you have questions about installing or using your Kontron Technology Product, check this User's Manual first – you will find answers to most questions here. To obtain support, please contact your local Distributor or Field Application Engineer (FAE).

#### **Before Contacting Support:**

Before requesting technical support be prepared to provide as much information as possible:

- CPU Board

- 1. Type.

- 2. Part-number (Number starting with "552" (GX1LCD/3.5") or "553" (GX1LCD/S)).

- 3. Serial Number.

- Configuration

- 1. CPU clock speed.

- 2. DRAM Type and Size.

- 3. BIOS Revision (Find the Version Info in the BIOS Setup in the Inside Section).

- 4. BIOS Settings different than Default Settings (Refer to the Software Manual).

- System

- 1. O/S Make and Version.

- 2. Driver Version numbers (Graphics, Network, and Audio).

- Attached Hardware: Harddisks, Floppy, LCD Panels etc.

## **Table of contents**

| 1.  |                                            | .1  |

|-----|--------------------------------------------|-----|

| 2.  | INSTALLATION PROCEDURE                     | .2  |

| 2.1 | Check the Kit Contents                     | . 2 |

| 2.2 | Installing the Board                       | .3  |

|     |                                            |     |

| 2.3 | LCD Panel Mounting Options                 |     |

| 2.4 | Requirement according to EN60950 :         | .5  |

| 3.  | SYSTEM SPECIFICATION                       | .6  |

| 3.1 | Configuration overview                     | 6   |

| 3.2 | Component main data                        | 8   |

| 3.3 | System overview                            | 11  |

| 3   | 3.1 CPU/GX1 and CS5530A                    | 11  |

| 3   | 3.2 XPRESS Graphics                        | 12  |

| 3   | 3.3 PCI-bus                                |     |

| 3   | 3.4 ISA bus                                | 13  |

| 3   | 3.5 SDRam interface                        | 13  |

| 3   | 3.6 Panel interface                        | 13  |

| 3   | 3.7 Audio                                  |     |

|     | 3.8 IDE interface                          |     |

| 3   | 3.9 USB                                    |     |

| 3   | 3.10 Ethernet                              |     |

|     | 3.11 Winbond W83877ATF                     |     |

|     | 3.12 Winbond W83977AF                      |     |

|     | 3.13 M-system Disk on Chip (GX1LCD/S only) |     |

|     | 3.14 Supervision                           |     |

|     | 3.15 PLD                                   |     |

| 4.  | SYSTEM RESOURCES                           | 16  |

| 4.1 | Memory Map                                 | 16  |

| 4.2 | I/O - Map                                  |     |

| 4.3 | Interrupt Usage                            |     |

|     |                                            |     |

| 4.4 | DMA-channel Usage                          | 33  |

| 5.  | CONNECTOR DEFINITIONS                      | 34  |

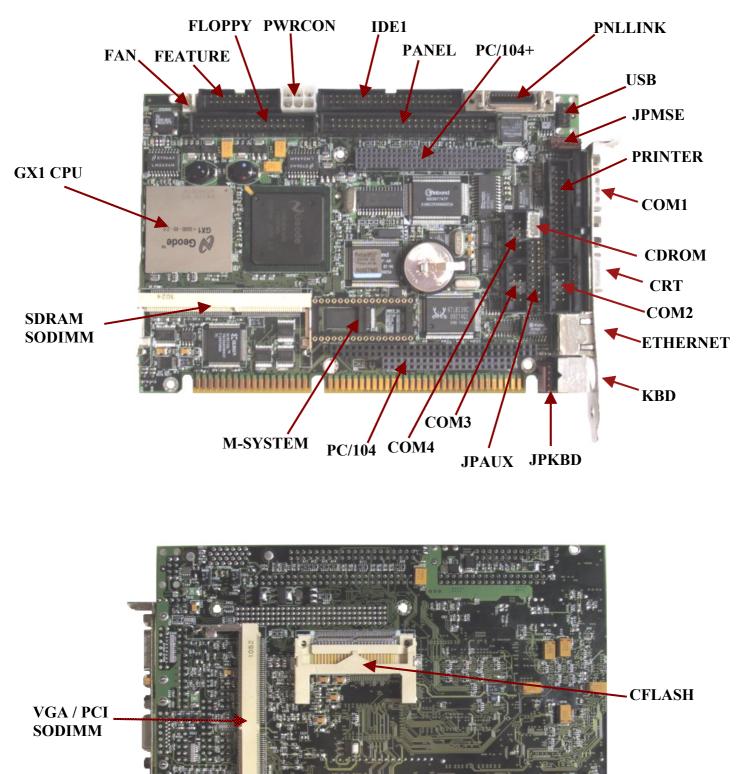

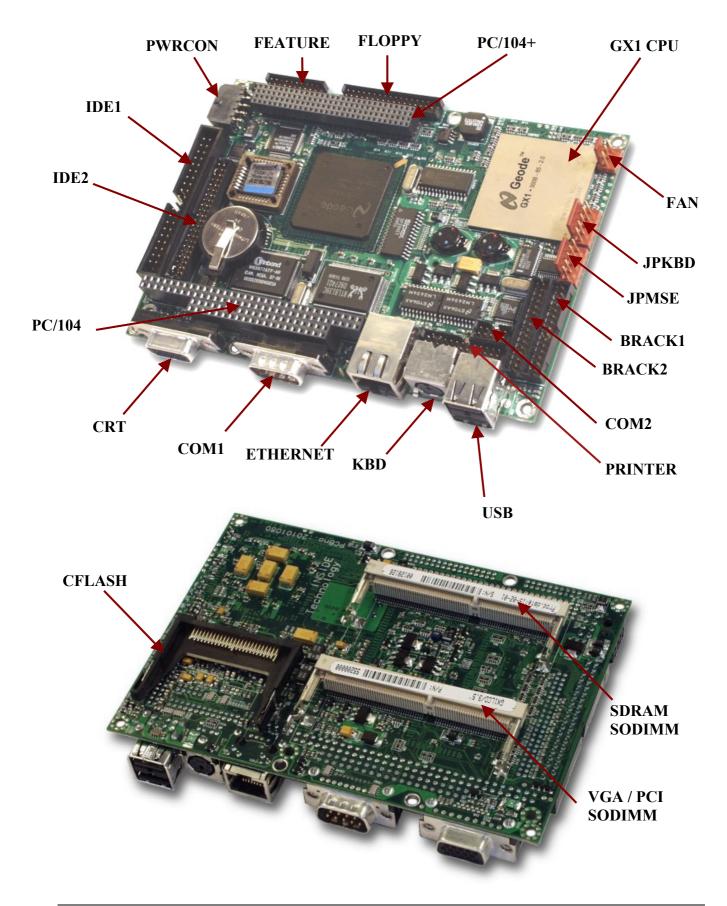

| 5.1 | Connector layout – GX1LCD/S                | 35  |

| 5.2 | Connector layout – GX1LCD/3.5"             | 36  |

| 5.3 P          | ower Connector (PWRCON)                              |    |

|----------------|------------------------------------------------------|----|

| 5.3.1          | GX1LCD/S Board                                       |    |

| 5.3.2          | GX1LCD/3.5 Board                                     |    |

| 5.3.3          | General Power Supply Requirements                    |    |

| 5.4 ŀ          | Keyboard and PS/2 mouse connectors                   |    |

| 5.4.1          | MINI-DIN combined keyboard and mouse Connector (KBD) |    |

| 5.4.2          | Pin-row Keyboard Connector (JPKBD)                   |    |

| 5.4.3          | Pin-row PS/2 Mouse Connector (JPMSE)                 |    |

| 5.5 I          | Display Connectors                                   |    |

| 5.5.1          | CRT Connector (CRT)                                  |    |

| 5.5.2          | Signal Description - CRT Connector                   |    |

| 5.5.3          | Flat Panel Connector (PANEL)                         |    |

| 5.5.4          | Signal Description - Flat Panel Connector            |    |

| 5.5.5          | Signal Configuration - Flat Panel Displays           |    |

| 5.5.6          | Panel Link (PNLLINK)                                 |    |

| 5.5.7          | Signal Description - Panel Link (PNLLINK)            |    |

| 5.6 F          | loppy Disk Connector (FLOPPY)                        |    |

| 5.7 H          | larddisk and Compact flash interface                 |    |

| 5.7.1          | IDE Hard Disk Connector (IDE1, IDE2)                 |    |

| 5.7.2          | Compact flash Connector (CFLASH)                     |    |

| 5.8 P          | rinter Port Connector (PRINTER)                      |    |

| 5.9 S          | erial Ports                                          |    |

| 5.9.1          | Serial Port 1 DB9 Connector (COM1) in RS232 Mode     |    |

| 5.9.2          | Serial Port 1 DB9 Connector (COM1) in RS422/485 Mode |    |

| 5.9.3          | Pin Header Serial Port 2 Connector (COM2)            |    |

| 5.9.4          | Pin Header Serial Port 3&4 Connector (COM3 & COM4)   |    |

| 5.10           | Ethernet connector (ETHERNET)                        |    |

| 5.11           | USB Connector (USB)                                  | 57 |

| 5.11.          |                                                      |    |

| 5.12           | GX1LCD/S Audio and IRDA connector (JPAUX)            |    |

| 5.12.          |                                                      |    |

| 5.12.          |                                                      |    |

| 5.12.          |                                                      |    |

| 5.12.          | •                                                    |    |

| 5.13           | GX1LCD/S CD-ROM input (CDROM)                        |    |

| 5.14           | GX1LCD/3.5" Bracket Module Interface                 |    |

| 5.14.          |                                                      |    |

| - 1 4          | Bracket Module Interface (BRACK1)                    |    |

| 5.14.          |                                                      |    |

| 5.14.<br>5.14. | 2 Bracket Module Interface (BRACK2)                  | 61 |

| 5.14.          | 2 Bracket Module Interface (BRACK2)                  |    |

| 5.16 | Feature Connector (FEATURE)                | 64 |

|------|--------------------------------------------|----|

| 5.17 | ISA bus connectors                         |    |

|      | 17.1 PC104 Connector (PC104XT & PC104AT)   |    |

| 5.1  | 17.2 PC-AT Edge Connector                  |    |

| 5.1  | 17.3 ISA signal description                |    |

| 5.18 | PC104+ PCI connector                       |    |

| 5.1  | 18.1 PC104+ PCI Connector                  | 71 |

| 5.1  | 18.2 Signal Description – PC104+ Connector | 72 |

| 6. I | MATING CONNECTOR LIST                      | 76 |

| 7. \ | WARRANTY                                   | 78 |

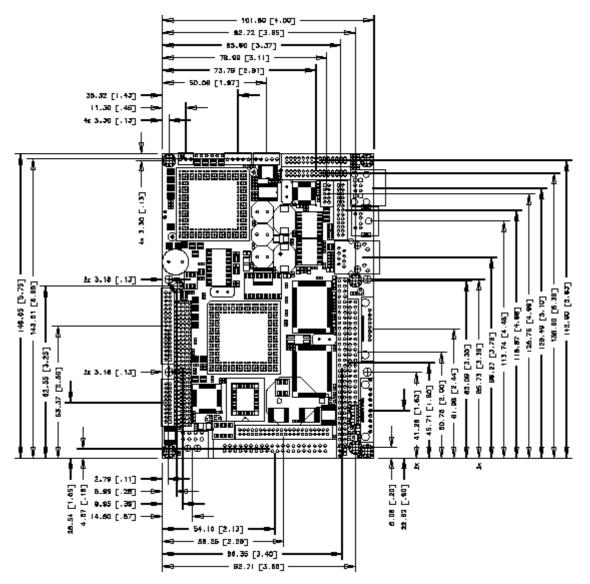

| 8. I | MEASUREMENT DRAWING (GX1LCD/S)             | 79 |

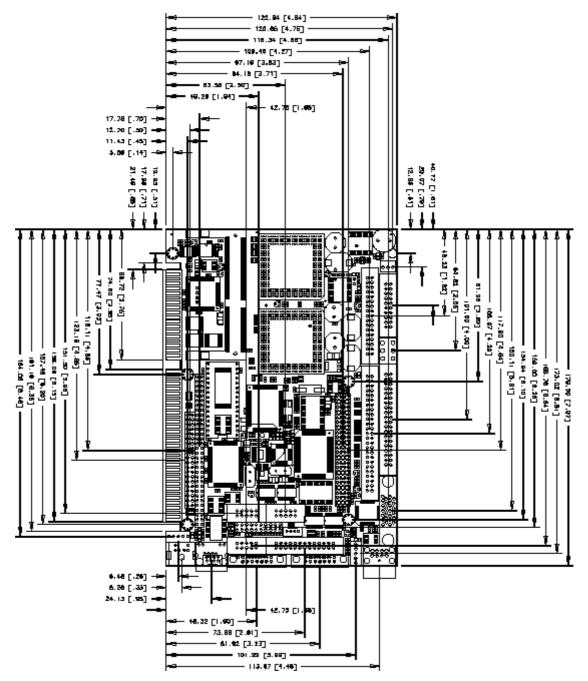

| 9. I | MEASUREMENT DRAWING (GX1LCD/3.5")          | 80 |

# 1. Introduction

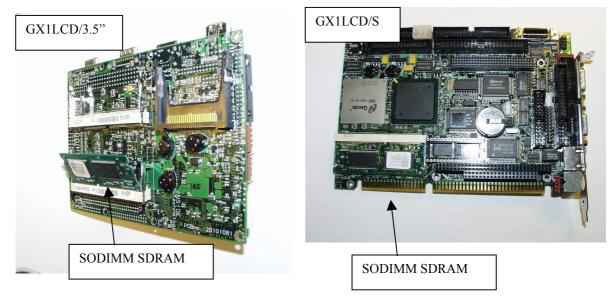

This manual describes the GX1LCD boards made by KONTRON Technology A/S. The boards will also be denoted GX1LCD or GX1 family if no differentiation is required.

All boards are based on the Geode GX1 processor with MMX enhancement from National<sup>®</sup>. This processor is abbreviated GX1 in this manual.

Use of this manual implies a basic knowledge of PC-AT hard- and software. This manual is focused on describing the GX1LCD Board's special features and is not intended to be a standard PC-AT textbook.

New users are recommended to study the short installation procedure stated in chapter 2 before switching-on the power.

All configuration and setup of the CPU board is either done automatically or by the user in the CMOS setup menus. No jumper configuration is required.

## 2. Installation procedure

## 2.1 Check the Kit Contents

The standard shipment should contain the following items:

- 1.) GX1LCD Board.

- 2.) Passive cooler (Mounted).

- 3.) Power Supply Adapter

For OEM shipments this contents list may be different than listed.

The optional accessory for the GX1 family is currently:

- 1. PC133 SDRAM module for SODIMM144 socket.

- 2. Audio Bracket for Audio Connector (JPAUX) for GX1LCD/S.

- 3. Audio Bracket for Audio Connectors (BRACK1, 2) for GX1LCD/3.5".

- 4. Panellink Module for installing in the Video Interface Module SODIMM144 connector.

- 5. DVI-S100 Module for installing in the Video Interface Module SODIMM144 connector.

- 6. LCDADPT 3V3 module for installing in the Video Interface Module SODIMM144 connector for support of Direct LCD connections on GX1LCD/3.5" boards.

- 7. DSTN module for installing in the Video Interface Module SODIMM144 connector for support of DSTN panels.

- 8. ATX power supply interface cable for GX1LCD/3.5" boards.

- 9. Standard 40-pin Internal IDE Harddisk Cable for Harddisk Connector (IDE1).

- 10. Harddisk Cable, 2mm to 3.5" Disks for Harddisk connector (IDE2) for GX1LCD/3.5".

- 11. Harddisk Cable, 2mm to 2.5" Disks for Harddisk connector (IDE2) for GX1LCD/3.5".

- 12. Standard 34-pin Internal Floppy Disk Drive Cable for Floppy Connector (FLOPPY) for GX1LCD/S.

- 13. Floppy Disk Drive Cable, 2mm, 34-pin, Internal for Floppy Connector (FLOPPY) for GX1LCD/3.5".

- 14. Y-cable for Keyboard and PS/2 Mouse for Keyboard Connector (KBD).

- 15. PS/2 Mouse Bracket for PS/2 Mouse Connector (JPMSE).

- 16. Serial and Parallel Port Bracket for Serial Com2 (COM2) and Parallel Port (PRINTER) Connectors for GX1LCD/S.

- 17. Serial Port Cable for COM3 and 4 (COM3, 4) for GX1LCD/S.

- 18. Serial Port Cable (2mm) for COM2 (COM2) for GX1LCD/3.5".

- 19. Parallel Port Cable (2mm) for PRINTER (PRINTER) for GX1LCD/3.5".

- 20. USB Bracket for USB Pin-header (USB) for GX1LCD/S.

- 21. GX1LCD Manual and Driver CDROM.

- 22. M-Systems DiskOnChip 2000 for DiskOnChip Socket (GX1LCD/S only).

- 23. Compact Flash card for insertion in Compact Flash Connector (CFLASH).

For an updated accessory list for the GX1LCD Product Family please check the Kontron Technology WorldWideWeb: <u>www.inside.dk</u> or contact the FAE. Updated drivers and manuals are also available here.

## 2.2 Installing the Board

To get the board running, follow these steps. The Board will have CPU and Cooler mounted when shipped from Kontron Technology.

- 1. Turn off the power supply.

- 2. Insert the SODIMM144 SDRAM module. Be careful to push it in the slot before rotating it into position. The locking mechanism will typically make a *click* when the module is locked in position. When running 100MHz clock speed on the SDRAM, the SDRAM must be rated for PC133. At 83MHz clock speed the SDRAM used can be PC100 rated.

- 3. Insert all external cables for hard disk, floppy, keyboard etc. except for flat panel. A CRT monitor must be connected in order to change CMOS settings to flat panel support.

- 4. Connect power supply to the board by the PWRCON connector and insert the board in a backplane if required (GX1LCD/S only).

- 5. Turn on the power.

- 6. Enter the BIOS setup by pressing the "F2" key during boot up. Setup the Processor clock speed in the Main menu. Refer to the Software Manual for details.

- 7. If Flat Panel Display is to be utilised, make sure the Panel type and Panel voltage in the BIOS setup in the Inside Utilities menu is correct before turning off the power and connecting the display cable. Refer to next Section for a description of the options for mounting a LCD Panel to the GX1LCD/3.5" and GX1LCD/S Boards.

**Note**: In case of corrupt CMOS settings the board may display an error message followed by "Press F1 to continue". To clear the non-PnP part of the CMOS (ESCD area – Extended System Configuration Data area) enter the Advanced menu and set "Reset Configuration Data" to *Yes*. At next boot the setting will be reset back to *No*.

To clear all CMOS settings, including Password protection, remove the battery for approximately 1 minute then reinsert it.

## 2.3 LCD Panel Mounting Options

The For GX1LCD/S boards flat panels can be connected directly to the onboard 50-pin LCD PANEL connector or via the Panellink connection PNLLINK connector (see Connector Layout).

For GX1LCD/3.5" boards flat panels can be connected using a module connected to the VGA SODIMM connector (<u>See Connector Layout</u>). Modules for Direct digital, Panellink, DVI- and DSTN connection are available from Kontron Technology.

Internal Panellink SODIMM Module for GX1LCD/3.5"

External Panellink SODIMM Module for GX1LCD/3.5"

50-pole LCD Connector SODIMM Module for GX1LCD/3.5"

Kontron Technology A/S.

## 2.4 Requirement according to EN60950 :

Users of 786LCD boards should take care when designing chassis interface connectors in order to fulfil the EN60950 standard :

When an interface/connector has a VCC (or other power) pin, that is directly connected to the VCC (or other) plane :

To protect the external power lines of peripheral devices the customer has to take care about

- That the wires have the right diameter to withstand the maximum available power.

- That the enclosure of the peripheral device fulfils the fire protecting requirements of IEC/EN 60950.

| CAUTION!                                                                                                                                                                                                           | VORSICHT!                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Danger of explosion if battery is incorrectly replaced.<br>Replace only with same or equivalent type<br>recommended by manyfacturer.<br>Dispose of used batteries according<br>to the manufacturer's instructions. | Explosionsgefahr bei unsachgemäßem Austausch der<br>Batterie.<br>Ersatz nur durch den selben oder einen vom<br>Hersteller empfohlenen gleichwertigen Typ.<br>Entsorgung gebrauchter Batterien nach<br>Angaben des Herstellers. |

| ADVARSEL!                                                                                                                                                                                                          | ADVARSEL                                                                                                                                                                                                                       |

| Lithiumbatteri – Eksplosionsfare ved fejlagtig<br>håndtering.<br>Udskiftning må kun ske med batteri<br>af samme fabrikat og type.<br>Levér det brugte batteri tilbage til leverandøren.                            | Eksplosjonsfare ved feilaktig skifte av batteri.<br>Benytt samme batteritype eller en tilsvarende<br>type anbefalt av apparatfabrikanten.<br>Brukte batterier kasseres i henhold til fabrikantens<br>instruksjoner.            |

| VARNING                                                                                                                                                                                                            | VAROITUS                                                                                                                                                                                                                       |

| Explosionsfara vid felaktigt batteribyte.<br>Använd samma batterityp eller en ekvivalent<br>typ som rekommenderas av apparattillverkaren.<br>Kassera använt batteri enligt fabrikantens<br>instruktion.            | Paristo voi räjähtää, jos se on virheellisesti asennettu.<br>Vaihda paristo ainoastaan laltevalmistajan<br>suosittelemaan<br>tyyppiln. Hävitä käytetty paristo valmistajan ohjeiden<br>mukaisesti.                             |

## Lithium Battery precautions:

## 3. System specification

The GX1LCD Family is based on the National Geode GX1 Processor with the chipset CS5530A. Configuration of the boards is done from the BIOS setup. Some features may additionally be reconfigured by user applications.

## 3.1 Configuration overview

The GX1LCD board family consist of four boards ranging from a low-cost board which provides basic PC functionality to a high-end board which provides improved interfacing to displays and improved performance as well as additional interfacing features. The configuration of these boards is listed below.

| Model                                        | GX1LCD/3.5"<br>Standard | GX1LCD/3.5"<br>Plus     | GX1LCD/S<br>Standard  | GX1LCD/S<br>Plus      |

|----------------------------------------------|-------------------------|-------------------------|-----------------------|-----------------------|

| Processor                                    | 200MHz                  | 300 MHz                 | 200 MHz               | 300 MHz               |

| BIOS                                         | Phoenix +               | Phoenix +               | Phoenix +             | Phoenix +             |

|                                              | Kontron<br>Technology   | Kontron<br>Technology   | Kontron<br>Technology | Kontron<br>Technology |

| Cooling                                      | Passive                 | Passive                 | Passive               | Passive               |

| Chipset                                      | National CS5530A        | National CS5530A        | National CS5530A      | National CS5530A      |

| DRAM Type                                    | SDRAM, PC133            | SDRAM, PC133            | SDRAM, PC133          | SDRAM, PC133          |

| DRAM (Max)                                   | 128 MB                  | 128 MB                  | 128 MB                | 128 MB                |

| Cache Type (GX1)                             | Level 1                 | Level 1                 | Level 1               | Level 1               |

| Cache (Kbyte)                                | 16 Kb                   | 16 Kb                   | 16 Kb                 | 16 Kb                 |

| M-Systems                                    | No                      | No                      | DOC2000 Socket        | DOC2000 Socket        |

| Disk on chip                                 |                         |                         |                       |                       |

| Compact Flash                                | CF Socket,              | CF Socket,              | CF Socket,            | CF Socket,            |

| Disk                                         | Type I, II              | Type I, II              | Type I                | Type I                |

| HDD                                          | 2 x 2 EIDE<br>(ATA-33)* | 2 x 2 EIDE<br>(ATA-33)* | 2 EIDE<br>(ATA-33)*   | 2 EIDE<br>(ATA-33)*   |

| FDD                                          | 2 x 1.44/2.88           | 2 x 1.44/2.88           | 2 x 1.44/2.88         | 2 x 1.44/2.88         |

| Bus                                          | ISA                     | ISA                     | ISA                   | ISA                   |

|                                              | PC/104                  | PC/104+                 | PC/104                | PC/104 +              |

| Graphics Ctrl.                               | National CS5530A        | National CS5530A        | National CS5530A      | National CS5530A      |

| Video RAM                                    | UMA                     | UMA                     | UMA                   | UMA                   |

|                                              | Up to 4MB               | Up to 4MB               | Up to 4MB             | Up to 4MB             |

| Display                                      | CRT/LCD                 | CRT/LCD                 | CRT/LCD               | CRT/LCD               |

|                                              | 18 bit                  | 18 bit                  | 18 bit                | 18 bit                |

| VGA / PCI<br>SODIMM Exten-<br>sion Connector | Yes                     | Yes                     | No                    | No                    |

| Model                             | GX1LCD/3.5"<br>Standard | GX1LCD/3.5"<br>Plus           | GX1LCD/S<br>Standard       | GX1LCD/S<br>Plus              |

|-----------------------------------|-------------------------|-------------------------------|----------------------------|-------------------------------|

| Resolution                        | 640 x 480               | 640 x 480                     | 640 x 480                  | 640 x 480                     |

|                                   | 800 x 600               | 800 x 600                     | 800 x 600                  | 800 x 600                     |

|                                   | 1024 x 768              | 1024 x 768                    | 1024 x 768                 | 1024 x 768                    |

|                                   | (16bpp)                 | (16bpp)                       | (16bpp)                    | (16bpp)                       |

|                                   | 1280 x 1024(8bpp)       | 1280 x 1024(8bpp)             | 1280 x 1024(8bpp)          | 1280 x 1024(8bpp)             |

| PanelLink, 24 bit                 | With VGA                | With VGA                      | No                         | No                            |

| MSB aligned                       | _                       | SODIMM Adapter                |                            |                               |

|                                   | Module                  | Module                        |                            |                               |

| USB                               | 12 MBit 2 Ch.           | 12 MBit 2 Ch.                 | 12 MBit 2 Ch.              | 12 MBit 2 Ch.                 |

| IrDA                              | Optional                | Optional                      | Optional                   | Optional                      |

| Ethernet                          | Realtek 8139C           | Realtek 8139C                 | Realtek 8139C              | Realtek 8139C                 |

|                                   | 10/100 MBit             | 10/100 MBit                   | 10/100 MBit                | 10/100 Mbit                   |

| Serial Ports                      | 2 x RS232C              | 2 x RS232C or                 | 2 x RS232C                 | 4 x RS232C or                 |

|                                   |                         | 1 x RS232C +<br>1 x RS422/485 |                            | 3 x RS232C +<br>1 x RS422/485 |

| Parallel Port                     | SPP/ECP/EPP             | SPP/ECP/EPP                   | SPP/ECP/EPP                | SPP/ECP/EPP                   |

| SW Watchdog                       | Yes                     | Yes                           | Yes                        | Yes                           |

| Temperature                       | No                      | Yes                           | No                         | Yes                           |

| Monitor                           | 110                     | 105                           | 110                        | 105                           |

| Power Supply                      | No                      | Yes                           | No                         | Yes                           |

| Monitoring                        |                         |                               |                            |                               |

| Fan Connector +                   | No                      | Yes                           | No                         | Yes                           |

| Supervision                       |                         |                               |                            |                               |

| Keyboard                          | PC/AT                   | PC/AT                         | PC/AT                      | PC/AT                         |

| Mouse                             | PS/2                    | PS/2                          | PS/2                       | PS/2                          |

| Speaker                           | On Board                | On Board                      | On Board                   | On Board                      |

| Sound, Line In/Out,               | No                      | Sound Bracket*                | No                         | Sound Bracket*                |

| Mic. In, Speaker<br>Out, CDROM In |                         |                               |                            |                               |

| Battery                           | Lithium                 | Lithium                       | Lithium                    | Lithium                       |

| Real Time Clock                   | Yes                     | Yes                           | Yes                        | Yes                           |

| General I/O                       | 8 (2x4)                 | 8 (2x4)                       | 8                          | 8                             |

| EMI                               | EN-55022/               | EN-55022/                     | EN-55022/                  | EN-55022/                     |

|                                   | EN-50082                | EN-50082                      | EN-50082                   | EN-50082                      |

| Operating Temp.                   | 0 - 60 °C.              | 0 - 60 °C.                    | $0 - 60 ^{\circ}\text{C}.$ | 0 - 60 °C.                    |

| Dimensions                        | 145 x 102 mm            | 145 x 102 mm                  | 179.5 x 123 mm             | 179.5 x 123 mm                |

|                                   | 5.7" x 4.0"             | 5.7" x 4.0"                   | 7.1" x 4.8"                | 7.1" x 4.8"                   |

\* O/S support restrictions apply; refer to Software manual for details.

## 3.2 Component main data

The main data for the functions and components on the board are listed below. Availability of some of the features depends on the configuration as listed above. For further details, refer to chapter 3.3 and the connector definitions in chapter 5.

| Processor                     | National Geode GX1processor with MMX enhancement (GX1)                                                                                                           |  |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Cache                         | Build in 16kB level 1 write-back cache in processor.                                                                                                             |  |  |

|                               | The GX1 processor does not support external cache.                                                                                                               |  |  |

| CPU Clock rate                | External: PCI clock (33MHz)                                                                                                                                      |  |  |

|                               | Internal: Configurable to 133, 200, and 300MHz* in the BIOS.<br>Maximum frequency depends on the processor mounted on the board.<br>(*depending on CPU mounted). |  |  |

| Chipset/Companion chip        | National CS5530A.                                                                                                                                                |  |  |

| System Clock Rate             | 33MHz PCI-bus. Internal clock multiplier in GX1 provides internal frequency.                                                                                     |  |  |

| SDRAM memory                  | SODIMM 144 pin form factor                                                                                                                                       |  |  |

|                               | Operating voltage: 3.3V                                                                                                                                          |  |  |

|                               | SDRAM modules must comply with the PC100 specification if<br>running at 83MHz SDRAM speed (Setup in the Main menu in the<br>BIOS).                               |  |  |

|                               | SDRAM modules must comply with the PC133 specification if<br>running at 100MHz SDRAM speed (Setup in the Main menu in the<br>BIOS).                              |  |  |

|                               | Up to 128MB supported.                                                                                                                                           |  |  |

| Plug and Play                 | PCI and ISA plug and play provided by BIOS                                                                                                                       |  |  |

| features                      | On-board I/O devices are reallocated if other devices are found.                                                                                                 |  |  |

| Graphics – XPRESS<br>Graphics | XPRESS Graphics controlled by the GX1 CPU and the Companion chip.                                                                                                |  |  |

|                               | CRT and TFT interface is provided.                                                                                                                               |  |  |

|                               | Refer to section 3.3.2 for details on operation modes.                                                                                                           |  |  |

|                               | See the software manual for details on driver installation and support for various operating systems.                                                            |  |  |

| Flat Panel Interface          | A flat panel connector is provided in order to interface to a wide range of displays.                                                                            |  |  |

|                               | Selection of display is performed in the BIOS, which will program refresh rates and timing of the graphics controller.                                           |  |  |

| PanelLink                     | Supports 24 bit display interface with dotclock up to 65MHz.<br>Transmission is performed at up to 650MHz on 4 differential lines at<br>up to 10m distance.      |  |  |

| Ethernet                      | 10Base-T and 100Base-T Ethernet is supported (IEEE802.3, [6]).                                                                                                   |  |  |

|                               | The Realtek 8139C Ethernet controller provides PCI bus-mastering operation for improved performance.                                                             |  |  |

| USB                                | USB controller integrated in the CS5530A companion chip is used.                                                                                        |  |  |  |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| USD                                | Two 12MBps USB channels are provided.                                                                                                                   |  |  |  |

|                                    | USB Legacy is currently not supported.                                                                                                                  |  |  |  |

|                                    |                                                                                                                                                         |  |  |  |

| M-systems Disk on<br>Chip          | A DIP32 connector is provided to support the M-systems Disk on<br>Chip 2000 flash disk system. GX1LCD/S Boards only.                                    |  |  |  |

| BIOS                               | Phoenix PICO BIOS v. 4.0.                                                                                                                               |  |  |  |

|                                    | VSA (Virtual System Architecture) code from Cyrix corp.                                                                                                 |  |  |  |

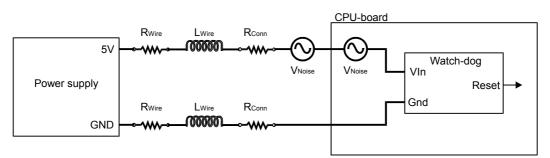

| Watchdog circuit                   | Supervision of power supply, fan-current and temperature. A watchdog timer is provided to reboot in case of system lockup.                              |  |  |  |

|                                    | These features are configured in the CMOS setup. See the software manual for details.                                                                   |  |  |  |

| Real-Time-Clock<br>and CMOS memory | System configuration, date and time are maintained by CMOS memory with battery backup.                                                                  |  |  |  |

| On-board Peripheal                 | AT-keyboard interface, PS/2 mouse interface,                                                                                                            |  |  |  |

| interfaces                         | RS232C interface. Charge pump driver requiring 5V only.                                                                                                 |  |  |  |

|                                    | RS232C or 485 interface. Charge pump driver requiring 5V only.                                                                                          |  |  |  |

|                                    | All RS232/RS485 ports are controlled by NS16550 comp. UART.                                                                                             |  |  |  |

|                                    | Parallel printer interface (Centronic, ECP, EPP mode).                                                                                                  |  |  |  |

|                                    | EIDE hard disk interface with support for Ultra DMA33 mode (Mode 2).                                                                                    |  |  |  |

|                                    | Compact flash connector for flash disk.                                                                                                                 |  |  |  |

|                                    | Floppy drive interface (2 x 360kB to 2.88MB)                                                                                                            |  |  |  |

| EMI                                | All Peripheral interfaces intended for connection to external equipment are EMI protected.                                                              |  |  |  |

| ISA-bus                            | The ISA bus is made available on the Edge connector and by the PC104 bus connector.                                                                     |  |  |  |

|                                    | ISA bus interface does not support Bus-mastering.                                                                                                       |  |  |  |

| PCI-bus                            | A PC104+ extension compliant to the <i>PC104Plus Specification v1.0</i> provides a PCI bus with support for up to 3 bus masters.                        |  |  |  |

|                                    | The bus operates at 3.3V signal levels. A 5V supply is provided in the connector. 3.3V supply is provided for light loads.                              |  |  |  |

| Power supply                       | External power supplies:                                                                                                                                |  |  |  |

|                                    | VCC Supply: +5V +5%                                                                                                                                     |  |  |  |

|                                    | +12V Supply +12V $\pm$ 5%                                                                                                                               |  |  |  |

|                                    | -12V Supply $-12V \pm 5\%$                                                                                                                              |  |  |  |

|                                    | All functions on the board can operate from a 5V supply only.<br>Connection of +/-12V can be made for external ISA/PC104 boards connected to the board. |  |  |  |

| Power Consumption | Approximately 4-8W depending on CPU and clock speed selected.                                                                                                                                                                        |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Battery           | Exchangeable 3.0V Lithium battery for onboard RTC.                                                                                                                                                                                   |  |  |  |

| Dattery           |                                                                                                                                                                                                                                      |  |  |  |

|                   | Manufacturer Toshiba / Part-number CR2032.                                                                                                                                                                                           |  |  |  |

|                   | Approximate 9 years retention.                                                                                                                                                                                                       |  |  |  |

|                   | Battery is protected against internal and external shorting according to UL requirements.                                                                                                                                            |  |  |  |

|                   | CAUTION: Danger of explosion if the battery is incorrectly<br>replaced. Replace only with the same or equivalent type<br>recommended by the manufacturer. Dispose of used batteries<br>according to the manufacturer's instructions. |  |  |  |

| Environmental     | Operating:                                                                                                                                                                                                                           |  |  |  |

| Conditions        | $0^{\circ}C - 60^{\circ}C$ operating temperature (forced cooling). It is the customer's responsibility to provide sufficient airflow to/from the board.                                                                              |  |  |  |

|                   | 10% - 90% relative humidity (non-condensing)                                                                                                                                                                                         |  |  |  |

|                   | Storage:                                                                                                                                                                                                                             |  |  |  |

|                   | -10°C – 85°C                                                                                                                                                                                                                         |  |  |  |

|                   | 5% - 95% relative humidity (non-condensing)                                                                                                                                                                                          |  |  |  |

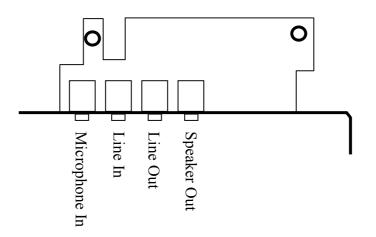

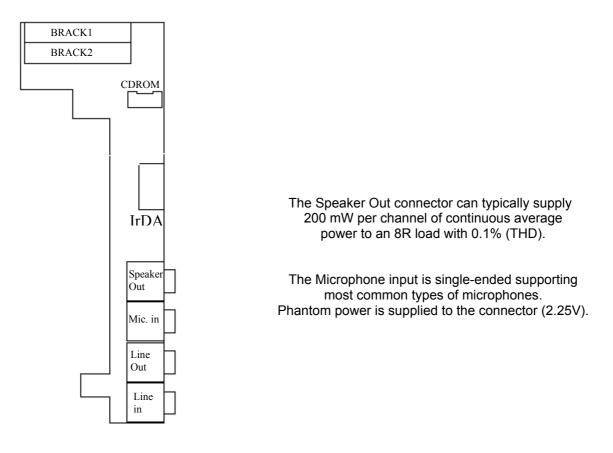

| Audio             | Audio based on AC97 codec. The following inputs/outputs are<br>provided: Line in, CD-ROM in, Microphone in (mono), Line out, and<br>Speaker out. Audio bracket is optionally supplied for mini-jack<br>connection.                   |  |  |  |

|                   | VSA (Virtual System Architecture) emulation of Sound Blaster 16.                                                                                                                                                                     |  |  |  |

| Dimensions        | GX1LCD/3.5": 145 mm x 102 mm x 30 mm (incl. Passive cooler).                                                                                                                                                                         |  |  |  |

|                   | GX1LCD/S: 179.5 mm x 123 mm x 26 mm (incl. Passive cooler).                                                                                                                                                                          |  |  |  |

## 3.3 System overview

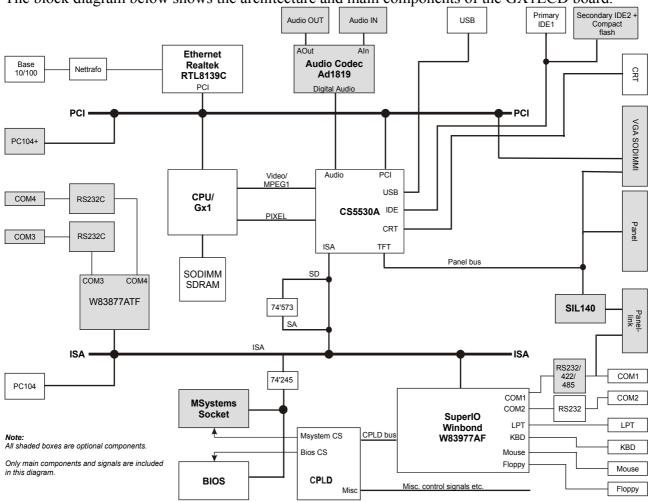

The block diagram below shows the architecture and main components of the GX1LCD board.

The two key components on the board are the National GX1 CPU and the CS5530A companion chip. These two devices provide the ISA and PCI bus to which all the major components are attached.

All shaded components are optional and are therefore only provided in some configurations.

The following sections will provide additional details about the functions of the board, shaded paragraphs indicate that the availability will depend on the model; check the differences in section 3.1.

## 3.3.1 CPU/GX1 and CS5530A

The National GX1 CPU along with the CS5530A companion chip provide the basic functionality and busses of the system:

- Interface to SDRam, 64 bit databus. PC100/ PC133 compliant SDRAM must be used.

- PCI interface provided by the GX1 CPU.

- PCI to ISA bridge provided by the 5530A.

- VGA-controller with video memory shared with system memory (UMA). The image data is transferred to the companion chip by means of the *Pixel* bus.

- A maximum of 4MB Video memory (UMA) can be shared with system memory. If a graphics resolution change requires an increased amount of graphics memory, the system must be rebooted, as there is no way system DRAM can be recovered from the operating system.

- CRT and TFT interface. Data is provided by the *Pixel* and *Video* interface from the CPU. The TFT interface and the SA part of the ISA bus share pins as described later.

- *Video* interface from the GX1 to the 5530. This data-stream is buffered and multiplexed with the Pixel bus for windowed video viewing. This interface may assist the processor in connection with motion picture decoding.

- USB integrated in the 5530.

- IDE interface supporting Ultra DMA. Two connectors are provided: A standard IDE interface on the primary controller and a compact flash and 40-pin connector on the secondary controller

- Digital audio interface to an AC97 compliant audio codec.

## **3.3.2 XPRESS Graphics**

As mentioned previously, the XPRESS Graphics is based on the GX1 CPU and the CS5530A Companion chip.

This graphics controller is very cost efficient since almost no additional components are required. This is achieved by using the SDRAM as frame-buffer and by integrating the graphics engine and display interface in the GX1 CPU and the CS5530A companion chip.

This controller provides a CRT as well as a TFT interface which support the modes listed below:

| Resolution | BPP   | Refresh/<br>Hz | Dotclock/<br>MHz | TFT bits | CRT | Simultanous<br>TFT/Panel |

|------------|-------|----------------|------------------|----------|-----|--------------------------|

| 640x480    | 8, 16 | 60             | 25,175           | 9,12,18  | Yes | Yes                      |

| 640x480    | 8, 16 | 72             | 31,5             | _        | Yes | No                       |

| 640x480    | 8, 16 | 75             | 31,5             | _        | Yes | No                       |

| 800x600    | 8, 16 | 60             | 40               | 9,12,18  | Yes | Yes                      |

| 800x600    | 8, 16 | 72             | 50               | _        | Yes | No                       |

| 800x600    | 8, 16 | 75             | 49,5             |          | Yes | No                       |

| 1024x768   | 8, 16 | 60             | 65               | 9,12,18  | Yes | No                       |

| 1024x768   | 8, 16 | 70             | 75               |          | Yes | No                       |

| 1024x768   | 8, 16 | 75             | 78,5             |          | Yes | No                       |

| 1280x768   | 8     | 60             | 108              | _        | Yes | No                       |

| 1280x768   | 8     | 75             | 135              | —        | Yes | No                       |

The Panel interface options are described in Section 2.3.

## 3.3.3 PCI-bus

The PCI-bus on the board is provided by the GX1 CPU and will always run at 33MHz.

The GX1 CPU provides support for up to 3 bus masters. Two of these bus master signals are used by the 5530 and the Realtek 8139C Ethernet controller.

In order to comply with the PC104+ specification additionally 3 sets of bus master signals are generated by means of an arbiter connected to a  $3^{rd}$  set of bus-master signals on the GX1 CPU. The arbitration algorithm being used provides a fair and equal arbitration for each of the PC104+ bus-masters.

The PCI interface provided in the PC104+ connector complies with the PC/104+ specification version 1.0 February 1997 [2].

The PC104+ specification essentially defines another physical interface to the PCI-bus defined in the PCI v2.1 specification [5].

#### **3.3.4** ISA bus

The 5530 companion chip provides a PCI-ISA bridge, which operate in slave mode. This means that all GX1LCD boards only support ISA slave mode.

ISA master mode allows an ISA board to grant the bus and get the bus master status. The bus master has the ability to generate bus cycles and transferring data without involvement of the CPU or DMA (Direct memory access).

ISA boards that utilise the bus master mode are less common today.

## 3.3.5 SDRam interface

This board uses SDRAM in the compact SODIMM-144 form factor. 3.3V SDRAM modules must be used.

For CPU / SDRAM Clock settings of 300MHz/ 100MHz PC133 SDRAM must be used. For CPU / SDRAM Clock settings of 300MHz/ 83MHz PC133 SDRAM must be used (see Software Manual).

### 3.3.6 Panel interface

An alternative display to the standard CRT monitor is a digital flat panel interface in which the color of each pixel is digitally encoded.

The panel data may be transferred in two ways:

- Parallel (available on PANEL connector) where the color of each pixel is transferred over a number of signal lines at rates up to 65MHz.

- Serial where the data is transferred over a few high speed digital lines at up to 650MHz. This interface is provided by the Silicon Image (http://www.siimage.com) SIL140 Panel Link transmitter.

The parallel interface is only suitable for small distances (less than 50 cm) and is typically implemented by means of ribbon cables. The user should consider the EMC design of the box and cabling when this interface is used.

It should also be noted that the signal level of these is 3.3V, but does comply to the TTL signal levels. Some (mostly older) displays require 5V signal level.

The Panel link interface transfers the data in low voltage differential mode through 4 twisted pair lines. This interface reduces EMC problems and allows display distances of up to 10m. Part of the COM1 interface is also provided in the Panel link connector in order to facilitate easy connection to a mouse, touch screen or other device (GX1LCD/S only).

More and more panels are now seen with Panel Link as their standard interface. If a Panel Link interface is not provided on the panel, a Panel Link receiver may be used to convert the serial data to a format suitable for the screen. For currently available Panel Link receivers please check our Web-site.

The Panel interface options are described in Section 2.3.

## **3.3.7** Audio

The CS5530A companion chip provides audio support by means of an AC97 codec interface. The audio codec provides mixing of the analog signals as well as Digital/analog conversion. The following analog interfaces are provided.

- Line-in, stereo.

- CR-ROM input, stereo.

- Microphone, single input with microphone bias circuit.

- Lineout, stereo.

- Speaker out, stereo. 2x0.5W in  $4\Omega$  on GX1LCD/S.

Access to the audio signals is provided by a pinrow (JPAUX) on GX1LCD/S or by a dedicated audio bracket.

Access to the audio signals is provided by a pinrow (BRACK1, 2) on GX1LCD/3.5" or by a dedicated audio bracket.

## 3.3.8 IDE interface

The CS5530S companion chip provides a primary as well as a secondary IDE controller with support of Ultra DMA33 mode and PCI bus mastering for the data transfer.

A standard IDC40 connector and an optional compact flash connector on the backside of the board provide access to these controllers.

### 3.3.9 USB

The USB interface provides two channels controlled by the CS5530A.

The signals are provided by means of a pinrow or by an USB bracket adapter on GX1LCD/S or by Type A USB Connector on GX1LCD/3.5".

USB Legacy is currently not supported.

### 3.3.10 Ethernet

The Ethernet interface is based on a Realtek 8139C Ethernet controller supporting 10MBit as well as 100Mbit Base-T interface.

The controller is attached to the PCI bus and uses PCI bus mastering for data transfer. The CPU is thereby not loaded during the actual transfer.

### 3.3.11 Winbond W83877ATF

This device provides additionally two RS232C COM-ports on GX1LCD/S Plus Boards (Total of 4 COM Ports). Operates in RS232 mode by means of a charge pump driver. Only 5V supply is required.

## 3.3.12 Winbond W83977AF

This is the main IO controller with the following features:

- COM1. A RS485/RS232 driver is used providing RS232, RS422/RS485. Selection of the mode is made in the BIOS. Driver uses charge pumps requiring only +5V.

- COM2. Operates in RS232 mode by means of a charge pump driver. Only 5V supply is required.

- LPT. Support for SPP, EPP and ECP modes.

- Keyboard interface.

- Mouse interface.

- IrDA interface for infrared communication. Maximum speed 115KBps. This interface shares the controller of COM2.

• NVRam with battery backup for BIOS configuration and real time clock.

Additionally, a number of general-purpose IO pins are used for the feature connector Generalpurpose IO pins and for various control signals on the board.

### 3.3.13 M-system Disk on Chip (GX1LCD/S only)

Access to the BIOS and M-system disk on chip socket is controlled by the CPLD on the board. In this way, it is possible to provide an address window for the disk on chip support. Information on DOC2000 devices may be found on http://www.m-sys.com.

The M-systems socket may additionally be used to bootstrap the system if the on-board BIOS should be erased. This requires an external flash BIOS (e.g Atmel 29C040A) inserted with a  $3.3K\Omega$  pull-down on the chip select signal (CS Pin 22, GND Pin 16). Contact Support for instructions on bootstrapping.

#### 3.3.14 Supervision

The Board supervision includes Power supplies, Board and CPU Temperature, and Fan rotation. A Watchdog Timer is provided in case of system lockup.

### 3.3.15 PLD

Some of the features mentioned require additional control and configuration signals not provided by the standard busses.

Examples of the functions of the PLD are:

- Supervision action on temperature, fan, and SW watch-dog alarms.

- CPU speed setting and other configurations eliminating the need for jumpers or dip-switches.

These configurations and features are encapsulated in the BIOS setup to provide an easy-to-use hardware independent interface. Please refer to the Software Manual User Utilities Section for further information.

# 4. System Resources

## 4.1 Memory Map

The following table indicates memory map for the **GX1LCD** boards. The address ranges specifies the runtime code length.

| Address Range      | Length     | Description                                                                  | Note |

|--------------------|------------|------------------------------------------------------------------------------|------|

| 00000000-000002FFh | 768 bytes  | BIOS Interrupt Vector Table                                                  |      |

| 00000300-000003FFh | 256 bytes  | BIOS Stack Area                                                              |      |

| 00000400-000004FFh | 256 bytes  | BIOS Data Area                                                               |      |

| 00000500-0009FFFFh | 639 Kbytes | Application Memory. Used by the operating system, device drivers and TSRs    |      |

| 000A0000-000BFFFFh | 128 Kbytes | Video memory page                                                            | 1    |

| 000C0000-000C7FFFh | 32 Kbytes  | Video BIOS ROM (CS5530)                                                      | 1    |

| 000C8000-000D7FFFh | 48 Kbytes  | Occupied by Network Boot Extension if enabled                                |      |

| 000D8000-000DFFFFh | 32 Kbytes  | Available for external ROM BIOS Extensions                                   |      |

| 000E0000-000E3FFFh | 16 Kbytes  | Occupied by M-System support on GX1LCD/S<br>Boards if enabled.               | 3    |

| 000E4000-000FFFFFh | 112 Kbytes | System BIOS ROM                                                              |      |

| 00100000-1FFFFFFFh | 511 Mbytes | Application Memory. Accessible through EMM-<br>handler or as Extended memory |      |

| FFFF0000-FFFFFFFh  | 64 Kbytes  | System BIOS ROM (mirrored)                                                   |      |

Note:

1. Used by the on-board VGA controller, if enabled.

- 2. Pressing Shift-F10 during boot and setting "Boot order" option enables net Boot ROM.

- 3. This area must be enabled in order to reprogram the BIOS on GX1LCD/S Boards.

## 4.2 I/O - Map.

On the GX1LCD board only ISA slave mode is supported.

The drive capabilities allow for up to five external ISA slots to be driven without external data buffers. The accessible I/O area on the ISA-bus is 64Kbytes with 16 address bits and the accessible Memory area is 16Mbytes with 24 address bits.

Certain I/O addresses are subject to change during boot as PnP managers may relocate devices or functions. The addresses shown in the table are typical locations

| I/O Port                               | Access   | Read/    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|----------------------------------------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                        |          | Write    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                        | 0000     | h – 001F | h are used by the 8237 Compatible DMA Controller 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| DMA Current A                          |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 0000h                                  | PCI      | R/W      | DMA channel 0 Address bits [15:0] : byte 0 (low byte), followed by byte 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 0001h                                  | PCI      | R/W      | DMA channel 0 Byte count [15:0] : byte 0 (low byte), followed by byte 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 0002h                                  | PCI      | R/W      | DMA channel 1 Address bits [15:0] : byte 0 (low byte), followed by byte 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 0003h                                  | PCI      | R/W      | DMA channel 1 Byte count [15:0] : byte 0 (low byte), followed by byte 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 0004h                                  | PCI      | R/W      | DMA channel 2 Address bits [15:0] : byte 0 (low byte), followed by byte 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 0005h                                  | PCI      | R/W      | DMA channel 2 Byte count [15:0] : byte 0 (low byte), followed by byte 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 0006h                                  | PCI      | R/W      | DMA channel 3 Address bits [15:0] : byte 0 (low byte), followed by byte 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 0007h                                  | PCI      | R/W      | DMA channel 3 Byte count [15:0] : byte 0 (low byte), followed by byte 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| DMA Status and Command Register Ch.3-0 |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 0008h<br>0008h                         | PCI      | R        | DMA channels 3-0 status registerBit 71Channel 3 requestBit 61Channel 1 requestBit 51Channel 0 requestBit 41Channel 0 requestBit 31Terminal count on channel 3Bit 21Terminal count on channel 1Bit 01Terminal count on channel 0DMA channels 3-0 command registerBit 70DACK# sense active low1DACK# sense active low1DACK# sense active highBit 50Late write selection1Extended write selection1Extended write selection1Rotating priority1Rotating priorityBit 30Bit 401Extended write selection1Extended write selection1Bit 40Fixed priority1Rotating priorityBit 301Normal timing1Compressed timingBit 10Bit 10Bit 10Bit 100Reserved. Must be 0.Bit 00Bit 00Bit 000Reserved. Must be 0. |  |  |  |  |

| DMA Request 1                          | Pagistar |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 0009h                                  | PCI      | W        | DMA write request register, Channels 3-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 00090                                  | PCI      | W        | DMA write request register, Channels 3-0         Bits 7-3       0       Reserved. Must be 0.         Bit 2       0       Resets individual DMA Channel Service SW Request         Bit 1-0       1       Sets the request bit.         00       DMA Channel 0 select         01       DMA Channel 1 select         10       DMA Channel 2 select         11       DMA Channel 3 select                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                      | gister           |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------|------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA Mask Re<br>000Ah | PCI              | W         | DMA channel 3-0 mask register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| UUUAII               | 101              | ٧V        | Bits 7-3 - Reserved. Must be 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                      |                  |           | Bit 2 0 Enable DREQ for the selected channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |